- 您现在的位置:买卖IC网 > Sheet目录3876 > PIC16F1526-I/PT (Microchip Technology)MCU 14KB FLASH 768B RAM 64-TQFP

207

7810C–AVR–10/12

Atmel ATmega328P [Preliminary]

21.2.1

TWI Terminology

The following definitions are frequently encountered in this section.

The PRTWI bit in “Minimizing Power Consumption” on page 40 must be written to zero to enable

the 2-wire Serial Interface.

21.2.2

Electrical Interconnection

As depicted in Figure 21-1, both bus lines are connected to the positive supply voltage through

pull-up resistors. The bus drivers of all TWI-compliant devices are open-drain or open-collector.

This implements a wired-AND function which is essential to the operation of the interface. A low

level on a TWI bus line is generated when one or more TWI devices output a zero. A high level

is output when all TWI devices tri-state their outputs, allowing the pull-up resistors to pull the line

high. Note that all AVR devices connected to the TWI bus must be powered in order to allow any

bus operation.

The number of devices that can be connected to the bus is only limited by the bus capacitance

limit of 400 pF and the 7-bit slave address space. A detailed specification of the electrical char-

acteristics of the TWI is given in “2-wire Serial Interface Characteristics” on page 311. Two

different sets of specifications are presented there, one relevant for bus speeds below 100 kHz,

and one valid for bus speeds up to 400 kHz.

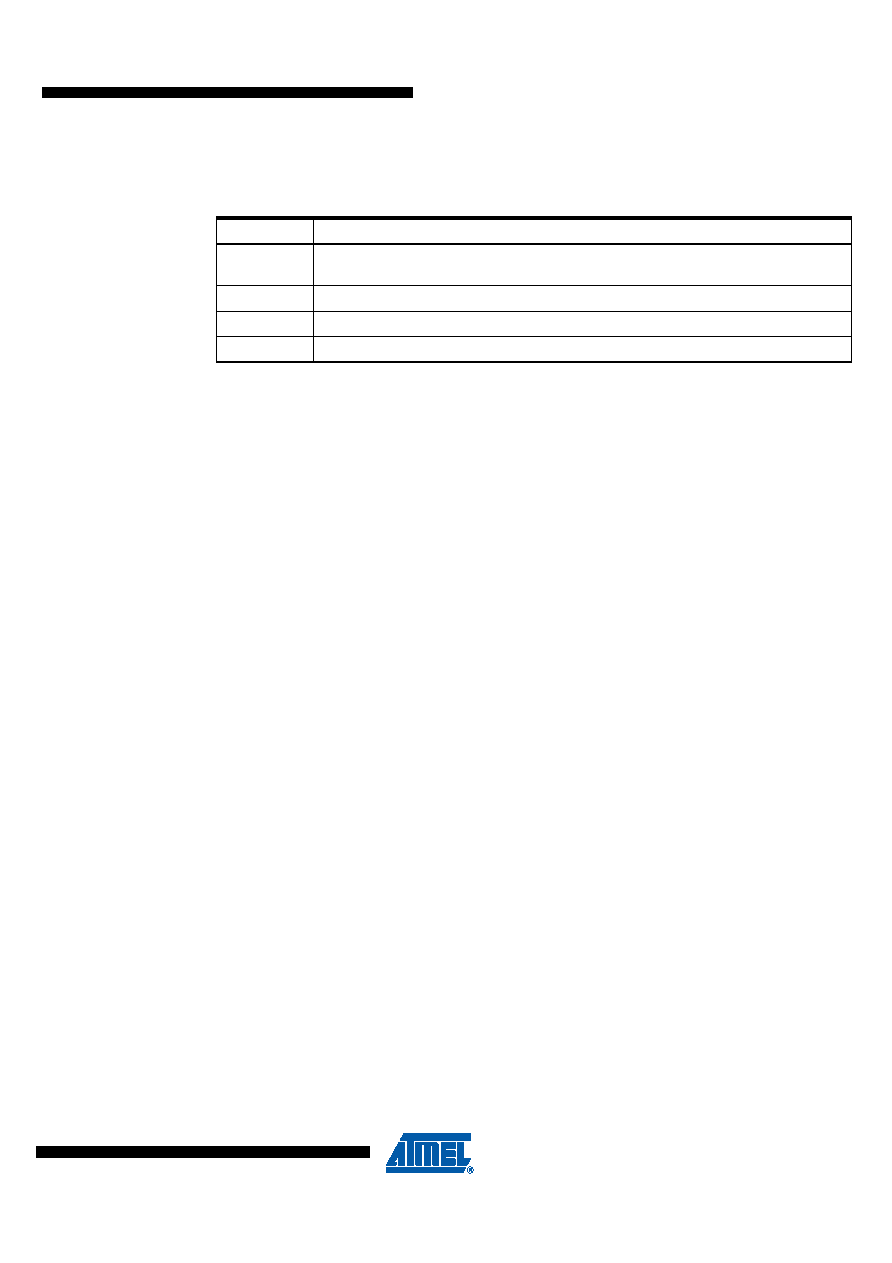

Table 21-1.

TWI Terminology

Term

Description

Master

The device that initiates and terminates a transmission. The Master also generates the

SCL clock.

Slave

The device addressed by a Master.

Transmitter

The device placing data on the bus.

Receiver

The device reading data from the bus.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC24F08KL401-I/SO

IC MCU 16BIT 8KB FLASH 20-SOIC

PIC18F13K50-I/MQ

IC PIC MCU FLASH 512KX8 20-QFN

PIC16F1934-I/PT

IC PIC MCU FLASH 256KX7 44-TQFP

PIC24F16KL402-I/SS

IC MCU 16BIT 16KB FLASH 28-SSOP

PIC16LF1934-I/PT

IC PIC MCU FLASH 256KX7 44-TQFP

PIC16C58B-20/P

IC MCU OTP 2KX12 18DIP

PIC18F24K20-I/SP

IC PIC MCU FLASH 8KX16 28-DIP

PIC16F1936-I/SP

IC PIC MCU FLASH 512KX14 28SPDIP

相关代理商/技术参数

PIC16F1526-I/PT

制造商:Microchip Technology Inc 功能描述:IC 8BIT MCU PIC16F 20 MHz 64-TQFP 制造商:Microchip Technology Inc 功能描述:IC, 8BIT MCU, PIC16F, 20MHz, TQFP-64

PIC16F1526T-I/MR

功能描述:8位微控制器 -MCU 14KB FL 768B RAM 10bit ADC 1.8-5.5V

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F1526T-I/PT

功能描述:8位微控制器 -MCU 14KB Flash RAM 768b nanoWatt

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F1527-E/MR

功能描述:8位微控制器 -MCU 28KB FL 1536B RAM 10bit ADC 1.8-5.5V

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F1527-E/PT

功能描述:8位微控制器 -MCU 14KB Flash RAM 768b nanoWatt

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F1527-I/MR

功能描述:8位微控制器 -MCU 28KB FL 1536B RAM 10bit ADC 1.8-5.5V

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F1527-I/MR

制造商:Microchip Technology Inc 功能描述:IC 8BIT MCU PIC16F 20 MHz 64-QFN 制造商:Microchip Technology Inc 功能描述:IC, 8BIT MCU, PIC16F, 20 MHz, 64-QFN; Controller Family/Series:PIC16F; Core Size:8bit; No. of I/O's:54; Program Memory Size:28KB; RAM Memory Size:1536Byte; CPU Speed:20MHz; Oscillator Type:External, Internal; No. of Timers:9 ;RoHS Compliant: No

PIC16F1527-I/PT

功能描述:8位微控制器 -MCU 14KB Flash RAM 768b nanoWatt

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT